Pacific

Northwest

NATIONAL LABORATORY

PNNL-35194

# Model Specification of VSC-HVDC Transmission (VHVDC\_A1)

January 14, 2026

DRAFT

## DISCLAIMER

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor Battelle Memorial Institute, nor any of their employees, makes **any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights.** Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof, or Battelle Memorial Institute. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

PACIFIC NORTHWEST NATIONAL LABORATORY

*operated by*

BATTELLE

*for the*

UNITED STATES DEPARTMENT OF ENERGY

*under Contract DE-AC05-76RL01830*

Printed in the United States of America

Available to DOE and DOE contractors from

the Office of Scientific and Technical Information,

P.O. Box 62, Oak Ridge, TN 37831-0062

[www.osti.gov](http://www.osti.gov)

ph: (865) 576-8401

fax: (865) 576-5728

email: [reports@osti.gov](mailto:reports@osti.gov)

Available to the public from the National Technical Information Service

5301 Shawnee Rd., Alexandria, VA 22312

ph: (800) 553-NTIS (6847)

or (703) 605-6000

email: [info@ntis.gov](mailto:info@ntis.gov)

Online ordering: <http://www.ntis.gov>

# **Model Specification of VSC-HVDC Transmission (VHVDC\_A1)**

September 2025

Pacific Northwest National Laboratory

Richland, Washington 99354

## Authors

### Names

Wei Du

Quan Nguyen

Sheik M Mohiuddin

Marcelo Elizondo

Richard Hoesel

Andreas Hanschick

Tuan Trinh

Eugen Starschich

Ara Panosyan

Pouyan Pourbeik

James Weber

Saurav Mohapatra

Jayapalan Senthil

Mengxi Chen

Juan Sanchez-Gasca

Jeff Bloemink

Fred Howell

Parag Mitra

Song Wang

Doug Tucker

Songzhe Zhu

### Organizations

Pacific Northwest National Laboratory

Pacific Northwest National Laboratory

Pacific Northwest National Laboratory

Pacific Northwest National Laboratory

Siemens Energy

Siemens Energy

Siemens Energy

Siemens Energy

Siemens Energy

Power and Energy, Analysis, Consulting and

Education (PEACE®) PLLC

PowerWorld

PowerWorld

Siemens

GE Vernova

GE Vernova (retired)

PowerTech Labs

PowerTech Labs

Electric Power Research Institute

Portland General Electric

Western Electricity Coordinating Council

GridBright, a Qualus Company

## 1. Acknowledgments

This material is based upon work supported by the U.S. Department of Energy's Grid Deployment Office (GDO) and Office of Energy Efficiency and Renewable Energy (EERE) under the Wind Energy Technologies Office. We would like to acknowledge the Western Electricity Coordinating Council (WECC) Modeling and Validation Subcommittee (MVS) for supporting this model development work.

DRAFT

## 2. Introduction

This document describes a standard library voltage source converter (VSC) high-voltage direct current (HVDC) model, namely, VHVDC\_A1. The initial version of this model specification was jointly developed by Pacific Northwest National Laboratory (PNNL) and Siemens Energy, and it was revised multiple times later to incorporate suggestions from WECC MVS members. Siemens Energy provided main control blocks to support the development of this model specification [1].

This standard library model is developed to help the utility industry better understand the VSC-based HVDC technology. The model could be used to represent equipment for transmission planning studies where vendor-specific models are not available. As equipment matures and improves, standard library models will be updated to capture the new functionalities of HVDC transmission technology. It is not intended that these models will always remain representative of all future HVDC technologies.

DRAFT

### 3. Model Description

This section describes the details of different applications and components of the HVDC model.

#### 3.1. Model Applications

The applications of the HVDC model include:

- 1) *Point-to-point connection within an ac grid – this will be referred to as an interconnection application herein:* in this application, Side-1 and Side-2 converters of the HVDC system connect to the same or isolated AC grids. Both converters operate in grid-following (GFL) mode to control voltage, power, and power factor at the AC Points of Interconnection (POIs) and DC voltage.

- 2) *Interconnecting an islanded generation source, such as a large islanded off-shore (or on-shore) wind farm – this will be referred to here as an islanded wind farm application:* in this application, Side-1 converter is assumed to connect to the islanded wind farm, while Side-2 converter connects to an AC grid. While Side-2 operates in GFL mode, Side-1 converter operates in V-F mode, i.e. constant AC voltage and frequency.

This model, in its present form, is not necessarily suitable for detailed analyses related to the dc side faults, or dynamics and disturbances within the islanded wind farm when used for islanded wind farm applications.

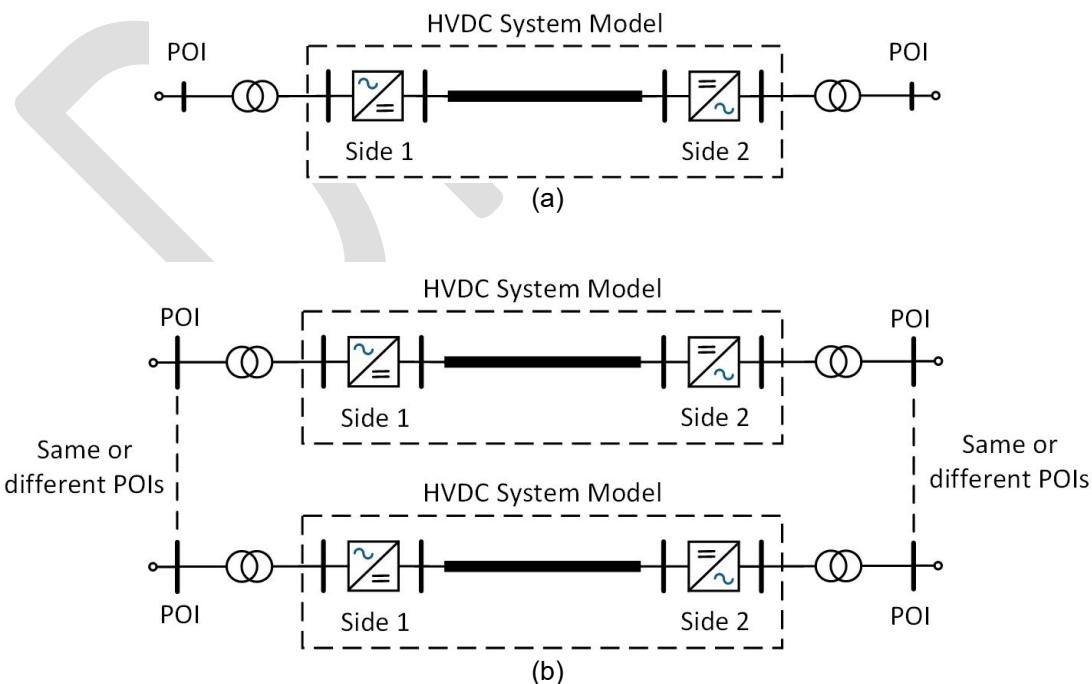

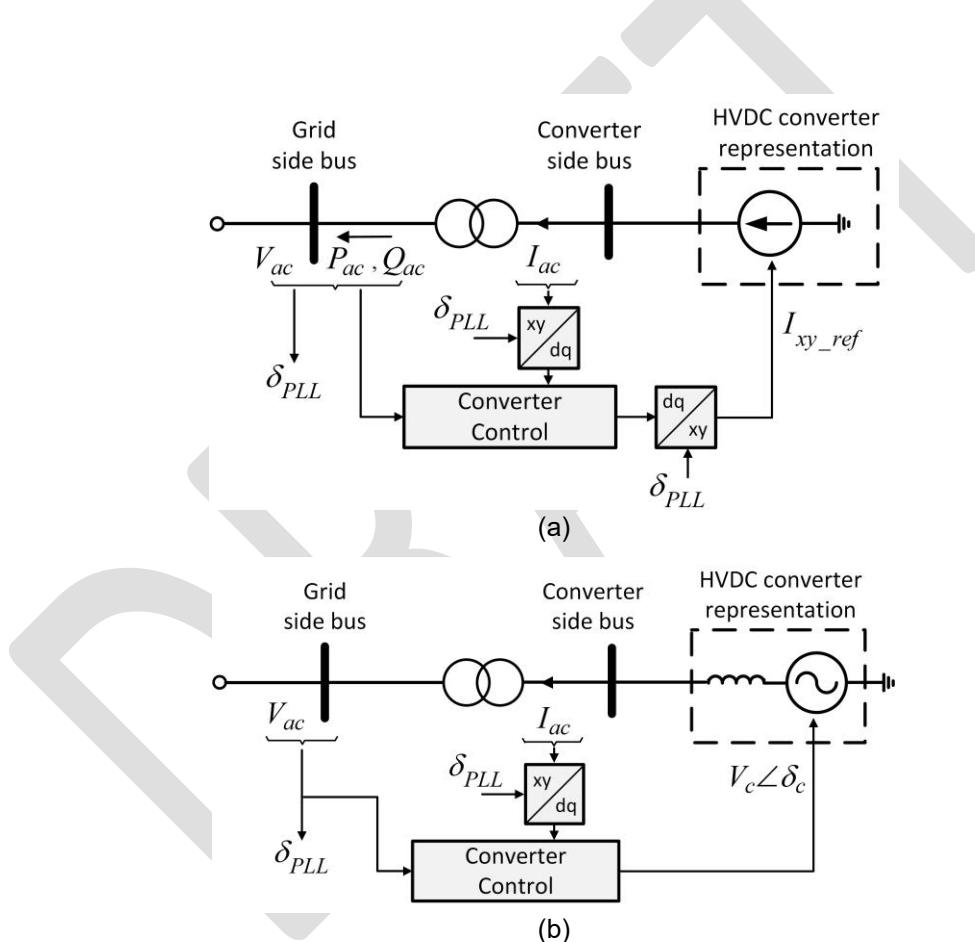

The model inherently represents the configuration and control of a point-to-point monopole HVDC link in Figure 1(a). A bipole HVDC system can be simulated by combining two such independent links in the system model, as shown in Figure 1(b). Note that the converter transformers are not included in the HVDC model.

Figure 1 Configurations of (a) a monopole HVDC link and (b) a bipole HVDC system, using the HVDC model

## 3.2. AC-DC Power Flow Model

The HVDC model requires an AC-DC power flow setup for the HVDC system, with the solved power flow solution used to initialize the model.

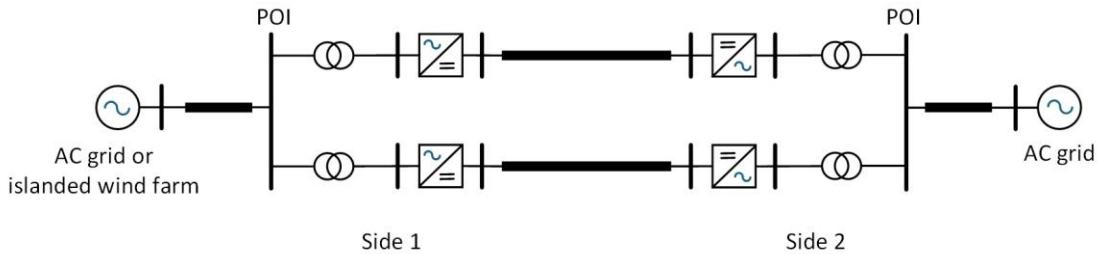

Figure 2 Power flow model of an example 2-terminal bipolar HVDC system.

The power flow model of an example 2-terminal bipolar HVDC system, which includes two separated links representing the positive and negative poles, is shown in Figure 2.

At the AC side, each HVDC converter is connected to the POI with the corresponding AC grid or islanded wind farm through a two-winding converter transformer. The converter-transformers must be explicitly modeled in power flow.

At the DC side, each DC line is represented by a resistance in the power flow model.

In addition to the topology and parameters of system components, the AC-DC power flow solution depends on the control modes of Side-1 and Side-2 converters, which are different in interconnection and islanded wind farm applications.

For active power control, it is required that one converter controls DC voltage and the other converter controls active power in the power flow setting. Thus, the corresponding DC voltage and AC power setpoints at these converters need to be provided for solving power flow. For interconnection and islanded wind farm applications, the following control options are allowed to setup the load flow model:

Option 1 (for interconnection applications): Side-1 converter controls DC voltage, and Side-2 converter controls AC active power with positive power set point (inverter mode) or negative power setpoint (rectifier mode).

Option 2 (for islanded wind farm applications): Side-1 converter controls AC active power with negative power set point, and Side-2 converter controls DC voltage.

Note that the arrangement in Option 2 is only for solving power flow. This control arrangement is a work-around solution for not having the V-F mode modeling in the commercial tools' AC-DC power flow formulation. On the other hand, the following control option for power flow setup is not allowed when using the developed model:

Option 3: Side-1 converter controls AC active power with positive power set point, and Side-2 converter controls DC voltage.

For reactive power control, each converter independently controls AC voltage, reactive power, or power factor at the POI, as long as the converter stays within its current limits. These reactive power control modes are modeled in the tools' AC-DC power flow formulation and reflected in the power flow solution.

### 3.3. Converter Interface with AC and DC Grids

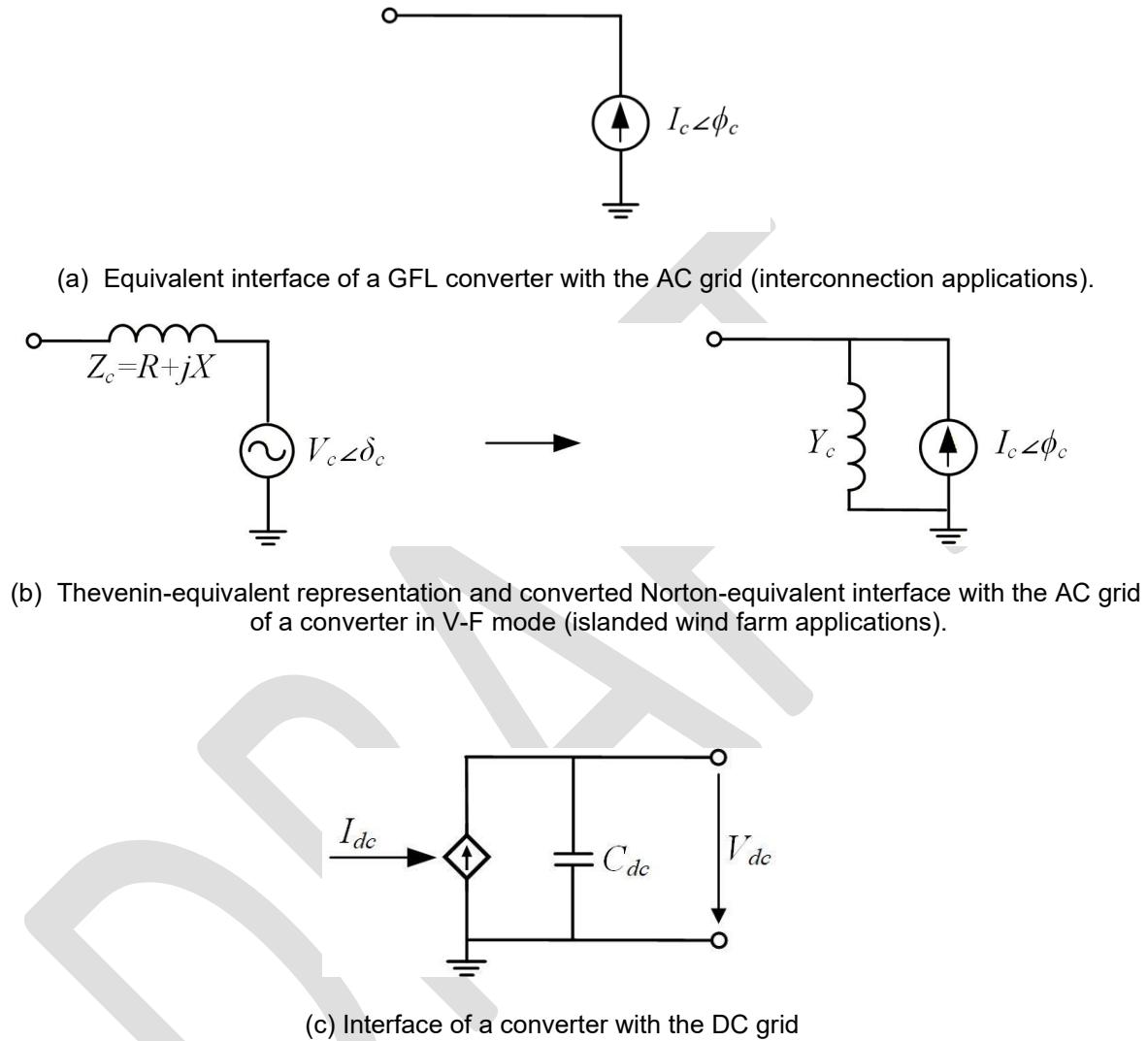

Figure 3 shows the interfaces of an HVDC converter with the interconnected AC and DC grids, which depend on the operating mode of the converter with respect to each grid.

With respect to AC grid, when the converter operates in GFL control strategy, it is readily represented as an ideal current source, as shown in Figure 3(a). On the other hand, when the converter operates in V-F control, such as for islanded wind farm applications, it behaves as a voltage source behind a Thevenin equivalent impedance. When interfacing with the AC network solution, this voltage source representation can be converted to a Norton equivalent current source, as shown in Figure 3(b).

With respect to the DC grid, the converter can be represented as a DC current source  $I_{dc}$ , as shown in Figure 3(c). This current  $I_{dc}$  can be calculated based on the power conservation for AC- and DC-side power injections and converter loss  $P_{loss}$  as follows:

$$I_{dc} = \frac{P_{dc}}{V_{dc}} = -\frac{P_{ac} + P_{loss}}{V_{dc}}. \quad (1)$$

In (1), converter loss  $P_{loss}$  is calculated as follows:

$$P_{loss} = \min (A_{loss} + B_{loss} |I_{dc}|, P_{loss\_min}) \quad (2)$$

where  $A_{loss}$  and  $B_{loss}$  are loss coefficients and  $P_{loss\_min}$  is the minimum loss, which are defined in the power flow model of the HVDC line.

Figure 3 Interface of converters with AC and DC grids corresponding to different operating modes at the AC and DC sides.

### 3.4. DC Line Model

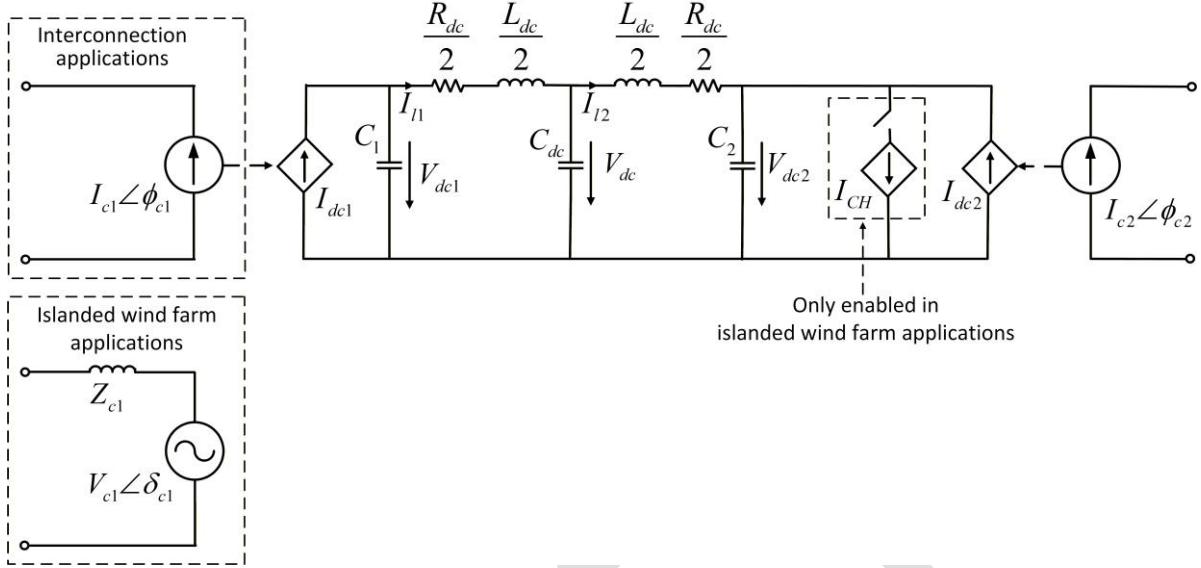

Figure 4 DC line model in an HVDC system model.

The DC transmission lines and cables are modelled as a standard DC line with total line resistance  $R_{dc}$ , line inductance  $L_{dc}$ , and equivalent capacitance  $C_{dc}$  at the middle of the line, as shown in Figure 4. At the DC side of each converter, there is an equivalent capacitance that represents the converter submodules' capacitances. The equivalent capacitances  $C_1$  and  $C_2$  at Sides 1 and 2 are independent parameters of the model. The calculation of  $C_1$  and  $C_2$  is given in the Appendix:

With the direction conventions of DC voltages and currents in Figure 4, the dynamics of DC quantities are as follows:

$$C_1 \frac{d(V_{dc1})}{dt} = I_{dc1} - I_{l1} \quad (3)$$

$$C_{dc} \frac{d(V_{dc})}{dt} = I_{l1} - I_{l2} \quad (4)$$

$$C_2 \frac{d(V_{dc2})}{dt} = I_{l2} - I_{CH} + I_{dc2} \quad (5)$$

$$\frac{L_{dc}}{2} \frac{d(I_{l1})}{dt} = V_{dc1} - V_{dc} - I_{l1} \frac{R_{dc}}{2} \quad (6)$$

$$\frac{L_{dc}}{2} \frac{d(I_{l2})}{dt} = V_{dc} - V_{dc2} - I_{l2} \frac{R_{dc}}{2} \quad (7)$$

In islanded wind farm applications where the wind farm is assumed to be located on Side 1, an additional DC chopper equivalent model is activated on Side 2. The DC chopper, designed to consume energy under a fault scenario at the AC side of Side-2 converter for avoiding a DC overvoltage, is modeled algebraically as an additional current source  $I_{CH}$  in this HVDC model.

### 3.5. Measurement Points and Phase-Locked Loop

Figure 5(a) shows the simplified control diagram with measurements for both Side-1 and Side-2 converters in interconnection applications or Side-2 converter in islanded wind farm applications, which operate in GFL mode with respect to the AC side. On the other hand, Figure 5(b) shows that only for Side-1 converter in islanded wind farm applications, which operates in V-F mode with respect to the AC side. In both cases, the voltage and power measurements are at grid side, i.e. primary side of the substation transformer. The current measurement is at the converter side, i.e. secondary side of the transformer. The output current source that represents the HVDC converter is also located at the converter side.

As mentioned earlier, the converter transformer must be explicitly modeled in power flow. Thus, the dynamic model will need six (6) parameters to define the from-bus, to-bus and transformer ID of the converter transformer on each side of the HVDC transmission system.

Figure 5 Simplified control diagram with measurements for a) Side-1 and Side-2 converters in interconnection applications or Side-2 converter in islanded wind farm applications, and b) Side-1 converter in islanded wind farm applications.

For both interconnection and islanded wind farm applications, converter control requires a dynamical estimation for the phase angle  $\delta_{PLL}$  of the terminal voltage, which is used to perform the  $xy$ -to- $dq$  transformation and vice versa. Instead of using a conventional Phase-Locked Loop (PLL), the estimated PLL angle  $\delta_{PLL}$  in this model is directly calculated from the measured phasor terminal voltage  $V_c = V_x + jV_y$  obtained from the converter interface with the AC network:

$$\delta_{PLL} = \frac{1}{1+T_{PLL, sync}S} \tan^{-1} \left( \frac{V_y}{V_x} \right). \quad (8)$$

Then, the  $dq$  currents can be calculated as follows:

$$I_d = I_x \cos \delta_{PLL} + I_y \sin \delta_{PLL}, \quad (9)$$

$$I_q = -I_x \sin \delta_{PLL} + I_y \cos \delta_{PLL}. \quad (10)$$

## 3.6. Side-1 Converter Model

The model and control of Side-1 converter are presented separately for interconnection and islanded wind farm applications as Side-1 converter operates in GFL and V-F mode, respectively.

### 3.6.1. Interconnection Applications

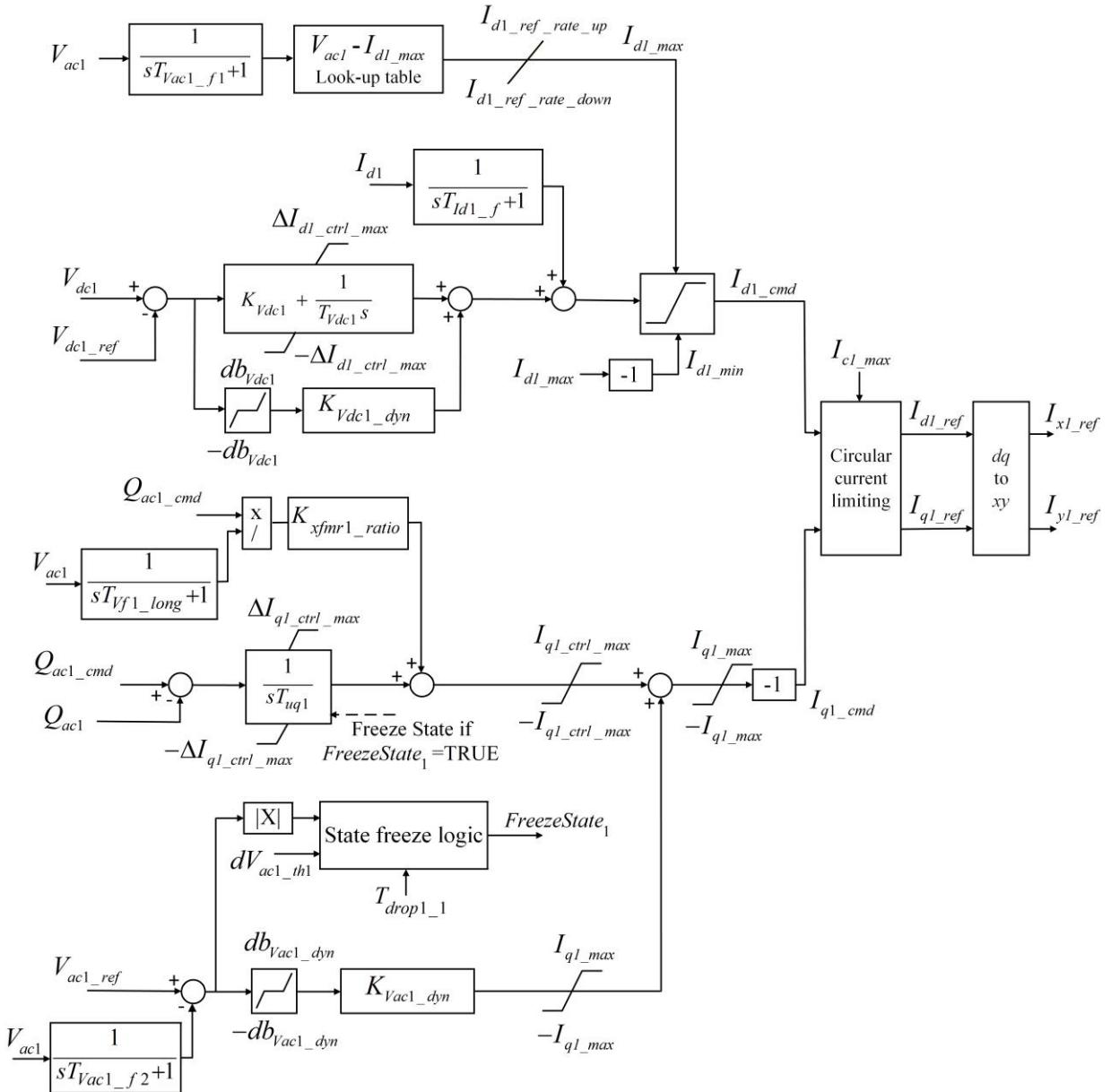

Figure 6 shows the main controller of Side-1 converter, which can be either one of the two converters in an HVDC system. In interconnection applications, converters at both sides operate in GFL mode, and it is assumed that Side-1 converter is responsible for regulating DC voltage. However, the converter at each side can be an inverter or rectifier.

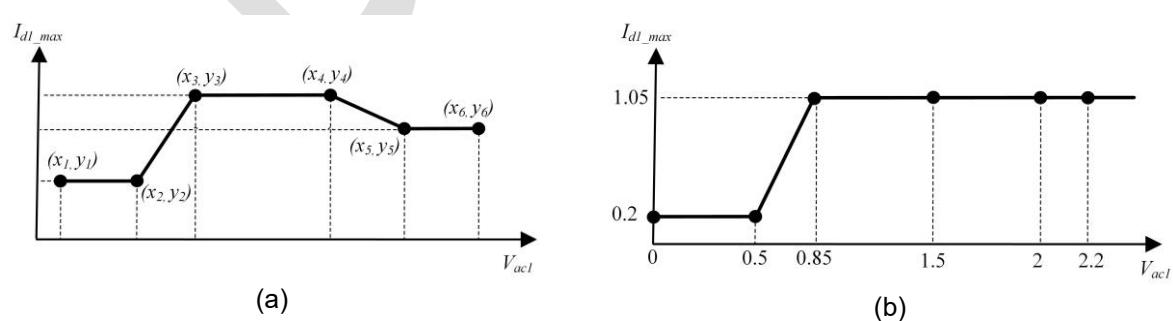

In the  $dq$  frame, the DC voltage control in the main control of Side-1 converter uses a feed-forward term based on the measured active-current component  $I_{d1}$ . The output of the DC-voltage controller is the active current command  $I_{d1\_cmd}$  is limited by the corresponding limits  $I_{d1\_max}$  and  $I_{d1\_min}$ . These limits are dynamically updated based on the measured active current  $I_{d1}$  and a pre-defined  $V_{ac1} - I_{d1\_max}$  look-up table, which is defined by a set of data points from the input model parameters as shown in [Figure 7](#). Under low-voltage conditions, the active current command  $I_{d1\_cmd}$  is intentionally reduced.

The main controller also uses the reactive power command  $Q_{ac1\_cmd}$ , which is the output of the outer reactive power control shown in Figure 8 as the input setpoint for generating the reactive current command  $I_{q1\_cmd}$ . Similar to the DC voltage control loop, there is a feed-forward term calculated based on the measured AC voltage and reactive power command  $Q_{ac1\_cmd}$ . However, during a significant terminal voltage sag or surge, the converter rapidly injects or absorbs reactive current to counteract the sudden voltage deviation. This fast response is enabled by activating proportional control while temporarily freezing the slower integration. In contrast, during the voltage recovery process, the proportional and integration controllers are deactivated and re-integrated, respectively. Note that the re-integration of the integration controller is delayed by a time-constant  $T_{drop1\_I}$ . Therefore, as indicated by the pseudo code in (11), the delay is applied only during the voltage rising edge, i.e., the recovery phase of the terminal voltage  $V_{ac1}$ .

Figure 6 Main converter controller of Side-1 converter in interconnection applications.

Figure 7 (a) General  $V_{ac1}$  -  $I_{d1\_max}$  curve of Side-1 converter, and (b) an example of the curve.

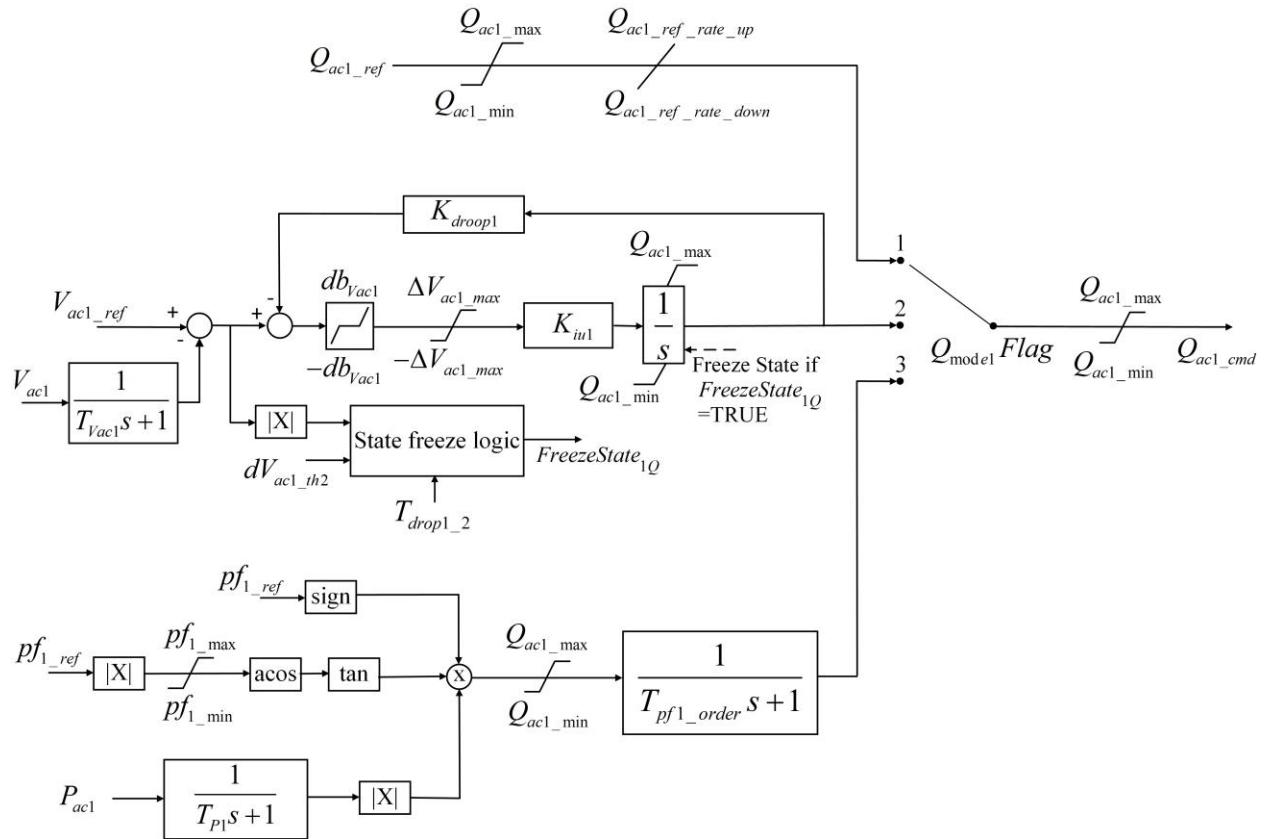

Figure 8 Main reactive power control of Side-1 converter in interconnection applications.

## Description of a State Freeze Decision Block

## Inputs from block diagram

**|X|** : input from block diagram into freeze decision block

**PresentTime** : the present time of the simulation

## Modal Input Parameters related to State Freeze Block

**dVActh** : deviation of X value at which state freezing occurs

**Tdrop** : seconds that must elapse after voltage recovers before the state will unfreeze

## Variables stored with the Model for a particular State Freeze Block

```

FreezeState : boolean // Initialize as FALSE - specifies

whether state is frozen

UnFreezeTimerActive : boolean // Initialize as FALSE - specifies

whether the UnfreezeTimer is active

UnFreezeTimerStart : single // Initialize as 0 stores the

time at which voltage first recovers

```

## Timer Logic that must be run each time-step of the numeric simulation

```

If |X| >= dVacth Then // Falling edge for low voltages because

deviation from Vacref is large

FreezeState = TRUE

UnFreezeTimerActive = FALSE // must reset this timer also,

otherwise the Unfreeze timer accumulates for repeated voltage changes

Else // "Rising" edge after a low voltages deviation because we are

back close to Vacref

```

```

If FreezeState Then // Need to see if we should unfreeze

If UnFreezeTimerActive = FALSE Then

UnFreezeTimerActive = TRUE // activate timer

UnFreezeTimerStart = PresentTime // start the timer by setting

to present time

Else

If (PresentTime - UnFreezeTimerStart) >= Tdrop Then

FreezeState = FALSE

UnFreezeTimerActive = FALSE // must reset for next use

EndIf

EndIf

EndIf

EndIf

```

In both normal and abnormal operating conditions, the generated active and reactive current commands  $I_{d1\_cmd}$  and  $I_{q1\_cmd}$  are jointly limited by a circular current limiting based on the maximum converter current  $I_{cl\_max}$ , which is a constant and defined as follows:

$$I_{cl\_max} = \max(I_{d1\_max}, I_{q1\_max}) . \quad (12)$$

The circular limiting strategy is defined as follows:

$$\begin{array}{c}

I_{d1\_cmd} + jI_{q1\_cmd} \xrightarrow{I_{cl\_cmd} < I_{cl\_max}} \bullet \\

I_{d1\_cmd} + jI_{q1\_cmd} \xrightarrow{I_{cl\_cmd} \geq I_{cl\_max}} \xrightarrow{k_1} I_{d1\_ref} + jI_{q1\_ref}

\end{array} \quad (13)$$

where:

$$I_{cl\_cmd} \angle \theta_{cl\_cmd} = I_{d1\_cmd} + jI_{q1\_cmd} , \quad (14)$$

$$k_1 = \frac{I_{cl\_cmd}}{I_{cl\_max}} . \quad (15)$$

Finally, the generated active- and reactive-current references  $I_{d1\_ref}$  and  $I_{q1\_ref}$  from the main control are used to synthesize the phasor reference current  $I_{x1\_ref} + jI_{y1\_ref}$  to interface with the AC grid as follows:

$$I_{x1\_ref} = I_{d1\_ref} \cos \delta_{1\_PLL} - I_{q1\_ref} \sin \delta_{1\_PLL} , \quad (16)$$

$$I_{y1\_ref} = I_{d1\_ref} \sin \delta_{1\_PLL} + I_{q1\_ref} \cos \delta_{1\_PLL} . \quad (17)$$

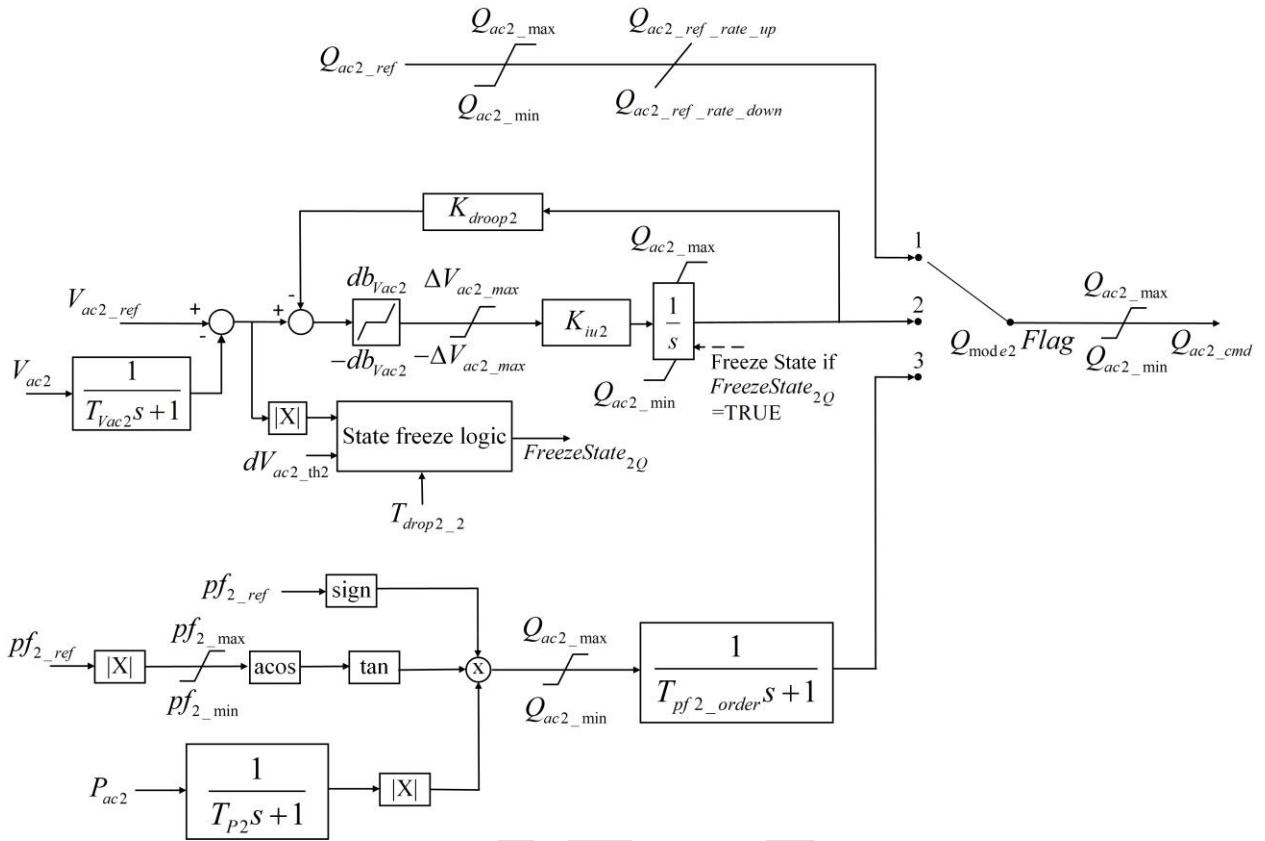

On the other hand, the outer reactive control in Figure 8 reflects the three options for Side-1 converter in controlling reactive power, AC voltage, and power factor. A reactive control mode can be selected by using  $Q_{mode\_SIFlag}$ . The output of this main reactive power control is the reactive power demand  $Q_{acl\_cmd}$  for the main converter control described above. In reactive power control mode, only the rate of change of the input reactive power reference  $Q_{acl\_ref}$  is limited. In AC voltage control mode, a  $Q$ - $V$  droop control is utilized with droop coefficient  $K_{droop\_SI}$  to generate the reactive power demand  $Q_{acl\_cmd}$ . In addition to the droop rule, the deadband applied for the AC voltage error before the integration also allows nonzero steady-state error if needed. Similar to the main converter control, under a significant voltage sag or surge, the integration of AC

voltage error is frozen for AC voltage regulation purpose. In power factor control mode, the reactive power demand  $Q_{ac1\_cmd}$  is computed directly from the input power factor reference  $p_{f1\_cmd}$  and the measured active power  $P_{ac1}$ . In all three reactive power control options, the output reactive power demand  $Q_{ac1\_cmd}$  is limited by a pre-defined limit.

### 3.6.2. Islanded Wind Farm Applications

In islanded wind farm applications, Side-1 converter operates in V-F mode by forming a voltage source at the AC side. As a result, Side-2 converter is responsible for controlling DC voltage, as shown in Section 3.7.

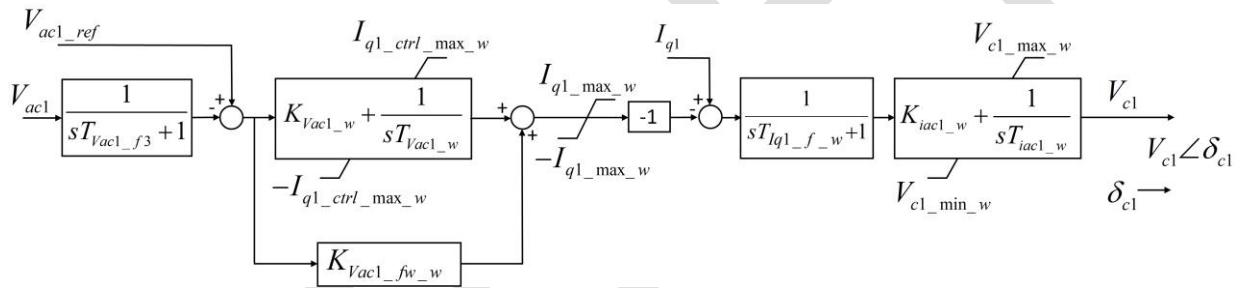

Figure 9 shows the main controller of Side-1 converter, which controls the terminal voltage magnitude  $V_{ac1}$  to track the reference  $V_{ac1\_ref}$ . This goal is achieved by using two cascaded PI controllers. The outer PI controller, supplemented by an additive linear term, eliminates steady-state terminal voltage error by generating the reference component of the converter current. The error between this reference current and measured current  $I_{q1}$  is the input of the inner PI controller that generates the reference converter voltage magnitude  $V_{cl1}$ . The phasor of the converter voltage is formed based on  $V_{cl1}$  and angle  $\delta_{cl1}$ , which is assumed to be constant.

Figure 9 Main converter controller of Side-1 converter in islanded wind farm applications.

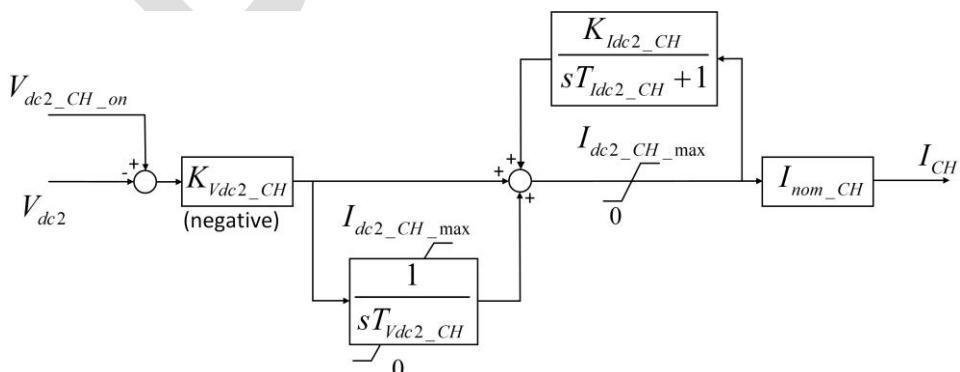

Figure 10 shows the DC chopper controller, which is only enabled in islanded wind farm applications to protect the HVDC system from a fault at the AC side of Side-2 converter. Under such a fault condition, Side-2 DC voltage  $V_{dc2}$  is expected to increase. The chopper controller is activated when  $V_{dc2}$  exceeds a pre-defined upper threshold  $V_{dc2\_CH\_on}$ , and it uses a negative gain and an integration to calculate the equivalent chopper current  $I_{CH}$ .

Figure 10 Chopper controller.

The chopper impact is modeled algebraically through the net effective DC source current, which is given as follows:

$$I_{dc2\_eff} = I_{dc2} - I_{CH}. \quad (18)$$

When the energy dissipation on the DC chopper exceeds a limit  $E_{CH\_max}$ , as defined in (19), the DC chopper is tripped:

$$\int_{T_0}^t (V_{dc2} I_{CH}) dt > E_{CH\_max}, \quad (19)$$

where  $T_0$  is the time instant when the DC chopper is enabled.

For islanded wind farm operation, after the chopper energy exceeds a specified limit because of a severe fault, the chopper and the HVDC line are tripped. Any subsequent tripping of other generation resources or additional corrective actions must be determined by the user (e.g., the transmission planner) or handled software tools

### 3.7. Side-2 Converter Model

In this section, Side-2 converter models for both interconnection and islanded wind farm applications are presented together as the converter operates in GFL mode in both cases.

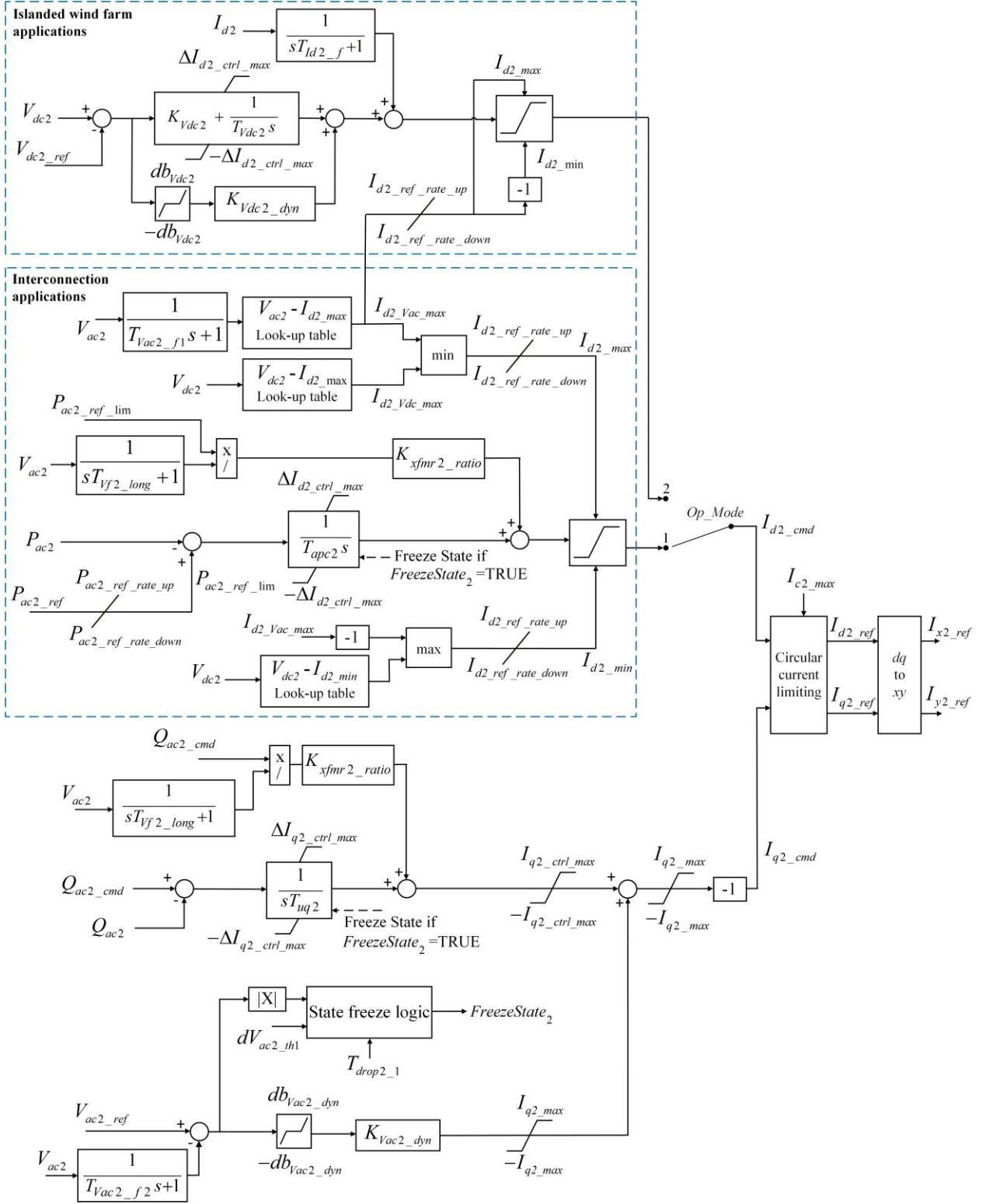

Figure 11 and Figure 12 show the main converter control and reactive power control of Side-2 converter. For interconnection and islanded wind farm applications, the first objective of Side-2 converter control is controlling AC active power and DC voltage, respectively. For both applications, the second objective is controlling reactive power through one of three possible options, similar to Side-1 reactive power control. The outputs of Side-2 converter control are the active- and reactive-current  $I_{d2\_ref}$  and  $I_{q2\_ref}$  to interface with the AC grid.

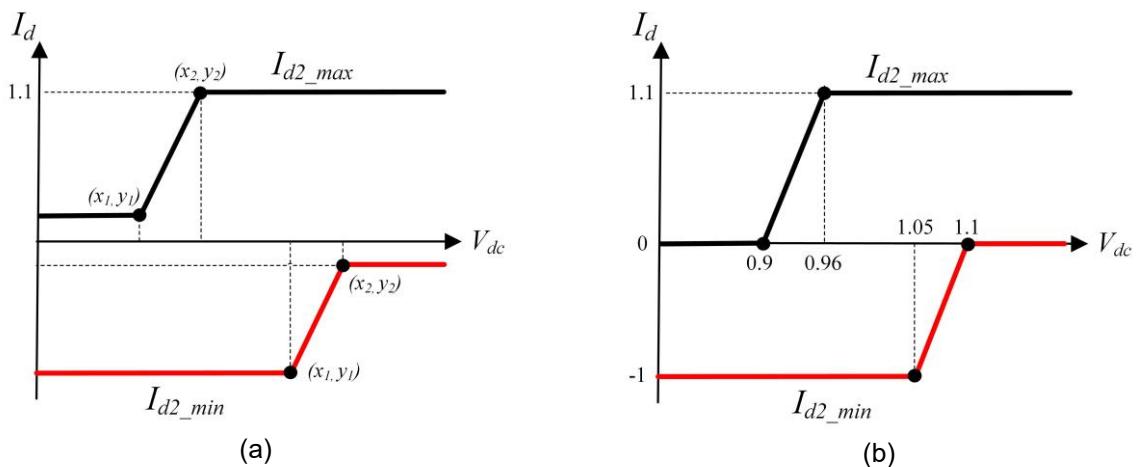

In Figure 11, both AC active power control and Side-2 DC voltage control include a feed-forward term of  $I_{d2}$  for fast transient response, along with an integration for AC active power error or a PI control for DC voltage error. Unlike DC voltage control, the AC active power uses a long time constant for filtering AC voltage, which leads to an approximately constant feed-forward term of  $I_{d2}$  during transient periods. Another difference is in the calculation of the limits for the output active current command  $I_{d2\_cmd}$ . While the DC voltage control only relies on the pre-defined  $V_{ac2} - I_{d2}$  look-up table, the AC active power control is based on both  $V_{ac2} - I_{d2}$  and  $V_{dc2} - I_{d2}$  look-up tables as DC voltage is not directly controlled in this mode. The curve resulting from the  $V_{ac2} - I_{d2}$  look-up table is similar to that of Side-1 converter, which is shown in Figure 7. The curves resulting from the  $V_{dc2} - I_{d2}$  look-up table provide both upper and lower limits of  $I_{d2}$  are shown in Figure 14. Again, these look-up tables are defined by sets of data points declared as the input parameters of the model.

On the other hand, the general structure of the reactive power control branch in Figure 11 and the main reactive power control of Side-2 converter in Figure 12 are identical to that of Side-1 converter in Figure 6 and Figure 8, respectively. Note that Side-1 and Side-2 converters control reactive power independently from each other, so their parameters can be set differently if needed. In addition, the reactive power control of Side-2 converter is similar for both interconnection and islanded wind farm applications.

Figure 11 Main converter control of Side-2 converter.

Figure 12 Main reactive power control of Side-2 converter.

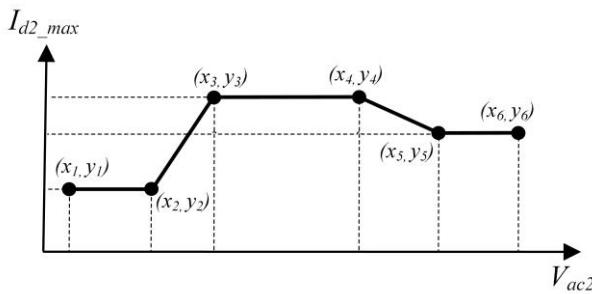

Figure 13 General  $V_{ac2}$  -  $I_{d2\_max}$  curve of Side-2 converter.

Figure 14 (a) General  $V_{dc2}$  -  $I_{d2\_max}$  and  $V_{dc2}$  -  $I_{d2\_min}$  curves of Side-2 converter, and (b) an example of the curves.

## 4. Dynamic Model Parameters

| #                                                                                     | Symbol                   | Description                                                                | Example Value |

|---------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------------------|---------------|

| Flags and general model information (Figure 2)                                        | <i>Op_Mode</i>           | 1: Interconnection - 2: Offshore (islanded wind farm)                      | 1             |

|                                                                                       | <i>Qmodel Flag</i>       | Side-1 Q control mode: 1 – Q, 2: Q-V, 3 : PF                               | 2             |

|                                                                                       | <i>Qmode2 Flag</i>       | Side-2 Q control mode: 1 – Q, 2: Q-V, 3 : PF                               | 2             |

|                                                                                       | <i>BusMain_1</i>         | Main bus bar bus number (Side 1)                                           | 110           |

|                                                                                       | <i>BusConverter_1</i>    | DC pole converter bus number (Side 1)                                      | 120           |

|                                                                                       | <i>IDXFMR_1</i>          | Transformer ID (Side1)                                                     | 1             |

|                                                                                       | <i>BusMain_2</i>         | Main bus bar bus number (Side 2)                                           | 210           |

|                                                                                       | <i>BusConverter_2</i>    | DC pole converter bus number (Side 2)                                      | 220           |

|                                                                                       | <i>IDXFMR_2</i>          | Transformer ID (Side2)                                                     | 1             |

| DC line model (Figure 4) and common parameters of two converters                      | <i>Vdc,rated</i>         | Rated DC voltage of the converters [kV]                                    | 525.0         |

|                                                                                       | <i>R1a</i>               | Side-1 arm resistance [ohm] (only used in islanded wind farm applications) | 0.05          |

|                                                                                       | <i>X1a</i>               | Side-1 arm reactance [ohm] (only used in islanded wind farm applications)  | 18.85         |

|                                                                                       | <i>R2a</i>               | Side-2 arm resistance [ohm] (only used in islanded wind farm applications) | 0.05          |

|                                                                                       | <i>X2a</i>               | Side-2 arm reactance [ohm] (only used in islanded wind farm applications)  | 18.85         |

|                                                                                       | <i>Ldc</i>               | DC line total inductance [mH]                                              | 129.3         |

|                                                                                       | <i>Cdc</i>               | DC line total capacitance [uF]                                             | 140.5         |

|                                                                                       | <i>C1</i>                | Equivalent capacitance of Side-1 converter [uF]                            | 221.7         |

|                                                                                       | <i>C2</i>                | Equivalent capacitance of Side-2 converter [uF]                            | 221.7         |

|                                                                                       | <i>TPLL, sync</i>        | PLL synchronization time constant [s]                                      | 0.05          |

| Main converter control on Side-1 converter in interconnection applications (Figure 6) | <i>TVac1_f1</i>          | First AC voltage filter time constant [s]                                  | 0.04          |

|                                                                                       | <i>TVac1_f2</i>          | Second AC voltage filter time constant [s]                                 | 0.02          |

|                                                                                       | <i>TIdl_f</i>            | Id filter time constant [s]                                                | 0.02          |

|                                                                                       | <i>TVfl_long</i>         | AC voltage filter long time constant [s]                                   | 60.0          |

|                                                                                       | <i>Tuq1</i>              | Integral time of iq controller [s]                                         | 10.0          |

|                                                                                       | <i>AIq1_ctrl_max</i>     | Maximum $\Delta$ lq control limit [pu]                                     | 0.3           |

|                                                                                       | <i>Iq1_ctrl_max</i>      | Maximum lq control limit [pu]                                              | 0.35          |

|                                                                                       | <i>Iq1_max</i>           | Maximum lq limit [pu]                                                      | 1.1           |

|                                                                                       | <i>KVac1_dyn</i>         | Vac error gain during faults                                               | 1.0           |

|                                                                                       | <i>dbVac1_dyn</i>        | Deadband Uac error in faults [pu]                                          | 0.1           |

|                                                                                       | <i>dVac1_th1</i>         | First high AC voltage error threshold [pu]                                 | 0.1           |

|                                                                                       | <i>Tdrop1_1</i>          | First delay of high AC voltage error [s]                                   | 0.01          |

|                                                                                       | <i>KVdc1_dyn</i>         | Feedforward Vdc gain                                                       | 6.0           |

|                                                                                       | <i>KVdc1</i>             | Gain of DC PI controller                                                   | 4.0           |

|                                                                                       | <i>TVdc1</i>             | Integral time constant of DC PI controller [s]                             | 20.0          |

|                                                                                       | <i>AIIdl_ctrl_max</i>    | Maximum $\Delta$ Id control limit [pu]                                     | 0.3           |

|                                                                                       | <i>dbVdc1</i>            | Deadband of DC voltage error [pu]                                          | 0.01          |

|                                                                                       | <i>Id1_ref_rate_up</i>   | $I_d$ setpoint ramp-up rate [pu/s]                                         | 9.0           |

|                                                                                       | <i>Id2_ref_rate_down</i> | $I_d$ setpoint ramp-down rate [pu/s]                                       | -9999         |

|                                                                                       | <i>TVac1</i>             | QControl Vac filter time constant [s]                                      | 0.02          |

|                                                                                              |                            |                                                         |         |

|----------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------|---------|

| Main Q control on Side-1 converter in interconnection applications (Figure 8)                | $T_{PI}$                   | QControl P filter time constant [s]                     | 0.5     |

|                                                                                              | $T_{pf1\_order}$           | Smoothing time constant of PF order [s]                 | 1.0     |

|                                                                                              | $db_{Vac1}$                | Deadband QV control [pu]                                | 0.0     |

|                                                                                              | $\Delta V_{ac1\_max}$      | Maximum AC voltage error in Q-V control [pu]            | 0.2     |

|                                                                                              | $K_{u1l}$                  | Proportional gain QV control [pu]                       | 20.0    |

|                                                                                              | $K_{droop1}$               | Inverse droop in deltaV/deltaQ [pu]                     | 0.1     |

|                                                                                              | $dV_{ac1\_th2}$            | Second high AC voltage error threshold [pu]             | 0.18    |

|                                                                                              | $T_{drop1\_2}$             | Second delay of high AC voltage error [s]               | 0.15    |

|                                                                                              | $pf1\_min$                 | Minimum PF value                                        | 0.9     |

|                                                                                              | $pf1\_max$                 | Maximum PF value                                        | 1.0     |

|                                                                                              | $Q_{ac1\_max}$             | Maximum reactive power [pu]                             | 0.33    |

|                                                                                              | $Q_{ac1\_min}$             | Minimum reactive power [pu]                             | -0.33   |

|                                                                                              | $Q_{ac1\_ref\_rate\_up}$   | Reactive power setpoint ramp-rate upper limit [pu/s]    | 9999    |

|                                                                                              | $Q_{ac1\_ref\_rate\_down}$ | Reactive power setpoint ramp-rate lower limit [pu/s]    | -9999   |

| Current limiting based on Vac on Side-1 converter in interconnection applications (Figure 7) | $V_{ac1\_Id1max\_X1}$      | Vac1_Id1max dynamic limits                              | 0.0     |

|                                                                                              | $V_{ac1\_Id1max\_X2}$      | Vac1_Id1max dynamic limits                              | 0.5     |

|                                                                                              | $V_{ac1\_Id1max\_X3}$      | Vac1_Id1max dynamic limits                              | 0.85    |

|                                                                                              | $V_{ac1\_Id1max\_X4}$      | Vac1_Id1max dynamic limits                              | 2.0     |

|                                                                                              | $V_{ac1\_Id1max\_X5}$      | Vac1_Id1max dynamic limits                              | 2.1     |

|                                                                                              | $V_{ac1\_Id1max\_X6}$      | Vac1_Id1max dynamic limits                              | 2.2     |

|                                                                                              | $V_{ac1\_Id1max\_Y1}$      | Vac1_Id1max dynamic limits                              | 0.2     |

|                                                                                              | $V_{ac1\_Id1max\_Y2}$      | Vac1_Id1max dynamic limits                              | 0.2     |

|                                                                                              | $V_{ac1\_Id1max\_Y3}$      | Vac1_Id1max dynamic limits                              | 1.1     |

|                                                                                              | $V_{ac1\_Id1max\_Y4}$      | Vac1_Id1max dynamic limits                              | 1.1     |

|                                                                                              | $V_{ac1\_Id1max\_Y5}$      | Vac1_Id1max dynamic limits                              | 1.1     |

|                                                                                              | $V_{ac1\_Id1max\_Y6}$      | Vac1_Id1max dynamic limits                              | 1.1     |

| Main controller on Side 1 in islanded wind farm applications (Figure 9)                      | $T_{Vac1\_f3}$             | Third AC voltage filter time constant [s]               | 0.0001  |

|                                                                                              | $K_{Vac1\_w}$              | Proportional gain voltage controller [pu]               | 4.0     |

|                                                                                              | $T_{Vac1\_w}$              | Integrator time constant voltage controller [s]         | 0.5     |

|                                                                                              | $I_{q1\_ctrl\_max\_w}$     | Maximum Iq in Vac control [pu]                          | 0.3     |

|                                                                                              | $K_{Vac1\_fw\_w}$          | Feed-forward gain in Vac control [pu]                   | 3       |

|                                                                                              | $I_{q1\_max\_w}$           | Maximum current Iq [pu]                                 | 1.1     |

|                                                                                              | $T_{Iq1\_f\_w}$            | Time constant of filter iq [s]                          | 0.02    |

|                                                                                              | $K_{iac1\_w}$              | Proportional gain current controller [pu]               | 0.25    |

|                                                                                              | $T_{iac1\_w}$              | Integration time constant current controller [s]        | 0.5     |

|                                                                                              | $V_{c1\_min\_w}$           | Minimum limit of offshore converter voltage [pu]        | -0.1    |

|                                                                                              | $V_{c1\_max\_w}$           | Maximum limit of offshore converter voltage [pu]        | 1.3     |

|                                                                                              | $V_{dc2\_CH\_on}$          | Chopper activation threshold voltage [pu]               | 1.035   |

| Chopper (Figure 10)                                                                          | $K_{Vdc2\_CH}$             | Proportional gain chopper control [pu]                  | -20.0   |

|                                                                                              | $T_{Vdc2\_CH}$             | Integrator time constant chopper control [s]            | 0.025   |

|                                                                                              | $I_{dc2\_CH\_max}$         | Maximum chopper current [pu]                            | 1.4     |

|                                                                                              | $K_{Idc2\_CH}$             | Proportional gain of chopper current control [pu]       | 0.9     |

|                                                                                              | $T_{Idc2\_CH}$             | Integrator time constant of chopper current control [s] | 0.15    |

|                                                                                              | $I_{nom\_CH}$              | Chopper nominal current [kA]                            | 1.8     |

|                                                                                              | $E_{CH\_max}$              | Maximum chopper energy [MJ]                             | 2,142.2 |

|                                                                                              | $T_{Vac2\_fl}$             | First AC voltage filter time constant [s]               | 0.04    |

|                                                        |                            |                                                         |       |

|--------------------------------------------------------|----------------------------|---------------------------------------------------------|-------|

| Main converter control on Side-2 converter (Figure 11) | $T_{Vac2\_f2}$             | Second AC voltage filter time constant [s]              | 0.02  |

|                                                        | $T_{Vf2\_long}$            | AC voltage filter long time constant [s]                | 60.0  |

|                                                        | $\Delta I_{d2\_ctrl\_max}$ | Maximum $\Delta I_d$ control limit [pu]                 | 0.3   |

|                                                        | $I_{d2\_ref\_rate\_up}$    | $I_d$ setpoint ramp-up rate [pu/s]                      | 5.0   |

|                                                        | $I_{d2\_ref\_rate\_down}$  | $I_d$ setpoint ramp-down rate [pu/s]                    | -9999 |

|                                                        | $T_{apc2}$                 | Integral time of active power controller [s]            | 20.0  |

|                                                        | $P_{ac2\_ref\_rate\_down}$ | Lower limit of active power setpoint ramp-rate [pu/s]   | -9999 |

|                                                        | $P_{ac2\_ref\_rate\_up}$   | Upper limit of active power setpoint ramp-rate [pu/s]   | 9999  |

|                                                        | $T_{ug2}$                  | Integral time of iq controller [s]                      | 10.0  |

|                                                        | $K_{Vac2\_dyn}$            | Vac error gain during faults                            | 1.0   |

|                                                        | $dV_{ac2\_th1}$            | First high AC voltage error threshold [pu]              | 0.1   |

|                                                        | $T_{drop2\_1}$             | First delay of high AC voltage error [s]                | 0.01  |

|                                                        | $db_{Vac2\_dyn}$           | Vac error deadband during faults [pu]                   | 0.1   |

|                                                        | $\Delta I_{q2\_ctrl\_max}$ | Maximum $\Delta I_q$ control limit [pu]                 | 0.3   |

|                                                        | $I_{q2\_ctrl\_max}$        | Maximum $I_q$ control limit [pu]                        | 0.35  |

|                                                        | $I_{q2\_max}$              | Maximum $I_q$ limit [pu]                                | 1.1   |

|                                                        | $T_{ldc2\_f}$              | ldc filter time constant [s]                            | 0.02  |

|                                                        | $K_{Vdc2\_dyn}$            | Feedforward Vdc gain [pu]                               | 6.0   |

|                                                        | $K_{Vac2}$                 | Gain of DC PI controller [pu]                           | 4.0   |

|                                                        | $T_{Vac2}$                 | Integral time constant of DC PI controller [s]          | 2.5   |

|                                                        | $db_{Vdc2}$                | Deadband of DC voltage error [pu]                       | 0.1   |

|                                                        | $I_{dc2\_ref\_rate\_up}$   | Maximum ramp-up rate of ldc [pu]                        | 9.0   |

|                                                        | $I_{dc2\_ref\_rate\_down}$ | Maximum ramp-down rate of ldc [pu]                      | -9999 |

| Main Q control on Side-2 converter (Figure 12)         | $T_{Vac2}$                 | Vac filter time constant [s]                            | 0.02  |

|                                                        | $T_{P2}$                   | P filter time constant [s]                              | 0.5   |

|                                                        | $T_{pf2\_order}$           | Smoothing time constant of PF order [s]                 | 1.0   |

|                                                        | $db_{Vac2}$                | Deadband of Q-V control [pu]                            | 0.0   |

|                                                        | $\Delta V_{ac2\_max}$      | Maximum AC voltage error in Q-V control [pu]            | 0.2   |

|                                                        | $dV_{ac2\_th2}$            | Second high AC voltage error threshold [pu]             | 0.18  |

|                                                        | $T_{drop2\_2}$             | Second delay of high AC voltage error [s]               | 0.15  |

|                                                        | $K_{iu2}$                  | Proportional gain Q-V control [pu]                      | 20.0  |

|                                                        | $K_{droop2}$               | Inverse droop in deltaV/deltaQ [pu]                     | 0.1   |

|                                                        | $pf2\_min$                 | Minimum PF value                                        | 0.9   |

|                                                        | $pf2\_max$                 | Maximum PF value                                        | 1.0   |

|                                                        | $Q_{ac2\_max}$             | Maximum reactive power [pu]                             | 0.33  |

|                                                        | $Q_{ac2\_min}$             | Minimum reactive power [pu]                             | -0.33 |

|                                                        | $Q_{ac2\_ref\_rate\_up}$   | Upper limit of reactive power setpoint ramp-rate [pu/s] | 9999  |

|                                                        | $Q_{ac2\_ref\_rate\_down}$ | Lower limit of reactive power setpoint ramp-rate [pu/s] | -9999 |

| Current limiting based on Vac on Side-2 converter      | $V_{ac2\_Id2max\_X1}$      | Vac2_Id2max dynamic limits                              | 0.0   |

|                                                        | $V_{ac2\_Id2max\_X2}$      | Vac2_Id2max dynamic limits                              | 0.5   |

|                                                        | $V_{ac2\_Id2max\_X3}$      | Vac2_Id2max dynamic limits                              | 0.85  |

|                                                        | $V_{ac2\_Id2max\_X4}$      | Vac2_Id2max dynamic limits                              | 2.0   |

|                                                        | $V_{ac2\_Id2max\_X5}$      | Vac2_Id2max dynamic limits                              | 2.1   |

|                                                        | $V_{ac2\_Id2max\_X6}$      | Vac2_Id2max dynamic limits                              | 2.2   |

|                                                        | $V_{ac2\_Id2max\_Y1}$      | Vac2_Id2max dynamic limits                              | 0.2   |

|                                                        | $V_{ac2\_Id2max\_Y2}$      | Vac2_Id2max dynamic limits                              | 0.2   |

|                                                               |                       |                            |      |

|---------------------------------------------------------------|-----------------------|----------------------------|------|

| (Figure 13Figure 7)                                           | $V_{ac2\_Id2max\_Y3}$ | Vac2_Id2max dynamic limits | 1.05 |

|                                                               | $V_{ac2\_Id2max\_Y4}$ | Vac2_Id2max dynamic limits | 1.05 |

|                                                               | $V_{ac2\_Id2max\_Y5}$ | Vac2_Id2max dynamic limits | 1.05 |

|                                                               | $V_{ac2\_Id2max\_Y6}$ | Vac2_Id2max dynamic limits | 1.05 |

| Current limiting based on Vdc on Side-2 converter (Figure 14) | $V_{dc\_Id2min\_X1}$  | Vdc2_Id2min dynamic limits | 1.05 |

|                                                               | $V_{dc\_Id2min\_X2}$  | Vdc2_Id2min dynamic limits | 1.1  |

|                                                               | $V_{dc\_Id2min\_Y1}$  | Vdc2_Id2min dynamic limits | -1.0 |

|                                                               | $V_{dc\_Id2min\_Y2}$  | Vdc2_Id2min dynamic limits | 0.0  |

|                                                               | $V_{dc\_Id2max\_X1}$  | Vdc2_Id2max dynamic limits | 0.9  |

|                                                               | $V_{dc\_Id2max\_X2}$  | Vdc2_Id2max dynamic limits | 0.96 |

|                                                               | $V_{dc\_Id2max\_Y1}$  | Vdc2_Id2max dynamic limits | 0.0  |

|                                                               | $V_{dc\_Id2max\_Y2}$  | Vdc2_Id2max dynamic limits | 1.1  |

DRAFT

## Appendix

### 1. Calculation of DC-side equivalent capacitances

The equivalent capacitances  $C_1$  and  $C_2$  at the DC side of the two converters are calculated as follows:

$$C_1 = \frac{6 \times C_{SM1}}{N_{SM1}}, \quad C_2 = \frac{6 \times C_{SM2}}{N_{SM2}}, \quad (20)$$

where  $C_{SM1}$  and  $C_{SM2}$  are the capacitances of each submodule at Sides 1 and 2, while  $N_{SM1}$  is  $N_{SM2}$  are the corresponding numbers of submodules, which can be calculated as follows:

$$N_{SM1} = \text{int}\left(\frac{V_{dc,rated}}{V_{SM,rated1}}\right), \quad N_{SM2} = \text{int}\left(\frac{V_{dc,rated}}{V_{SM,rated2}}\right), \quad (21)$$

where  $N_{SM1}$  and  $N_{SM2}$  are the numbers of submodules, while  $V_{SM,rated1}$  and  $V_{SM,rated2}$  are the corresponding rated voltages of the submodules at Sides 1 and 2. On the other hand,  $V_{dc,rated}$  is the rated DC voltage of the HVDC line, which is one input of the model parameters.

## References

[1] Siemens Energy, “HVDCPL2 - Model description - PSS/E Model Siemens Energy HVDC PLUS”, February 2024. (Unpublished)

DRAFT