# Memorandum

March 18<sup>th</sup>, 2019

| SUBJECT: | TEST PROTOCOL FOR BENCHMARKING OF DER_A MODEL<br>WITHIN CMPLDW MODEL ACROSS SOFTWARE PLATFORMS |

|----------|------------------------------------------------------------------------------------------------|

| CC:      | Pouyan Pourbeik, PEACE-PLLC, WECC LMTF, NERC LMTF                                              |

| FROM:    | Deepak Ramasubramanian, Parag Mitra, Anish Gaikwad, Electric Power<br>Research Institute       |

| TO:      | WECC REMTF                                                                                     |

This document describes the proposed test protocol for benchmarking the working of the composite load model with the presence of the DER\_A model across multiple software platforms for use in positive sequence time domain simulations.

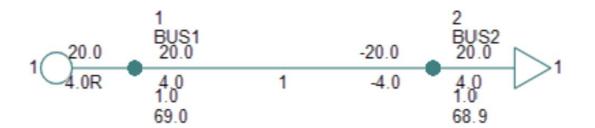

Figure 1 shows the test system setup that will be used for the benchmarking process while Table 1 tabulates the network details.

Figure 1Benchmark test system

Table 1Details of the network

|   | From | From Bus | То  |             |               |               | Charging B |

|---|------|----------|-----|-------------|---------------|---------------|------------|

|   | Bus  | Name     | Bus | To Bus Name | <b>R</b> (pu) | <b>X</b> (pu) | (pu)       |

| ſ |      | BUS1     |     | BUS2        |               |               |            |

|   | 1    | 69.000   | 2   | 69.000      | 0.0025        | 0.01          | 0          |

The source at Bus 1 will be modeled as a play-in voltage source. The load at Bus 2 will consist of 30 MW of constant power load (to be represented by the CMPLDW model) and 10 MW of DER (to be represented by the DER\_A model)

In this round of benchmark testing, the load will always be set at a non-zero value. It is expected that the validation of the code transfer for inclusion of the DER\_A model within the composite load model has already been carried out in each software platform along the lines of [1].

Table 2 tabulates the various tests that will be performed in this round of testing the model. Detailed description of some of the tests are provided after the table

| <u>Test number</u> |   | Description                                                                               |                                                          |  |

|--------------------|---|-------------------------------------------------------------------------------------------|----------------------------------------------------------|--|

|                    | А |                                                                                           | Load composition<br>being only Motor A<br>and with DER_A |  |

| Test 1             | В | Play-in a voltage<br>sag immediately<br>followed by a<br>voltage swell. This              | Load composition<br>being only Motor B<br>and with DER_A |  |

|                    | С | voltage waveform<br>would cause partial<br>voltage trip to occur<br>in DER_A              | Load composition<br>being only Motor C<br>and with DER_A |  |

|                    | D |                                                                                           | Load composition<br>being only Motor D<br>and with DER_A |  |

| Test 2             | А | Play-in a voltage<br>waveform which<br>would cause trip and<br>reconnection of<br>Motor A | Load composition<br>being only Motor A<br>and with DER_A |  |

|                    | В | Play-in a voltage<br>waveform which<br>would cause stall<br>and restart of Motor<br>D     | Load composition<br>being only Motor D<br>and with DER_A |  |

Table 2 List of various tests to be performed

| Te     | Test 3 |                                                                                                         | Load composition<br>being 50% Motor A,<br>50% Motor D, and<br>DER_A |

|--------|--------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

|        | А      | With load composition being                                                                             | Load = 30 MW,<br>DER = 1 MW                                         |

|        | В      | 10% Motor A, 10%<br>Motor B, 5% Motor<br>C, 40% Motor D,                                                | Load = 30 MW,<br>DER = 10 MW                                        |

|        | С      | 15% static load,<br>20% power<br>electronic load, and                                                   | Load = 30 MW,<br>DER = 30 MW                                        |

| Test 4 | D wi   | with DER_A, apply<br>a 0.1s fault on Bus 2<br>with fault X =                                            | Load = 30 MW,<br>DER = 45 MW                                        |

|        | E      | 0.005pu                                                                                                 | Load = 1 MW, DER<br>= 75 MW                                         |

|        | F      | Same fault<br>conditions as above,<br>but reactance<br>between bus 1 and<br>bus 2 increased to<br>0.5pu | Load = 1 MW, DER<br>= 75 MW                                         |

## Test Number 1

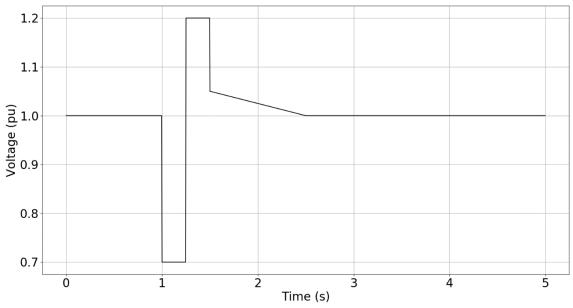

The play-in waveform for this test is as shown in Figure 2. A voltage sag of 0.7pu is applied at 1.0s for a duration of 15 cycles on 60 Hz. Immediately after that, the voltage is raised to 1.2pu for another 15 cycles of 60 Hz. The recovery level after the high voltage event is 1.05pu with a ramp time of 1.0s for the voltage to come back to 1.0pu.

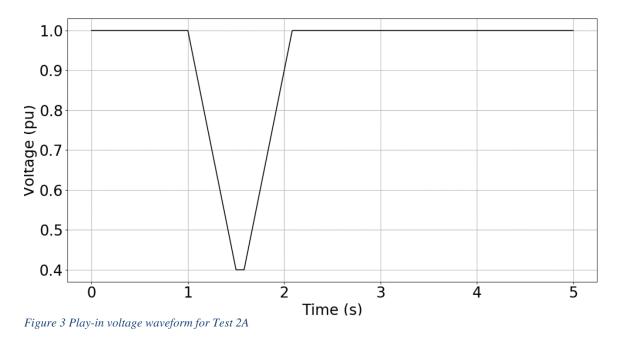

#### Test Number 2A

The play-in waveform for this test is as shown in Figure 3. At 1s, the voltage is reduced from 1 pu to 0.4 pu over 0.5s, held at 0.4 pu for 5 cycles at 60 Hz, and ramped back to 1 pu in 0.5s. The simulation is run for till 5s

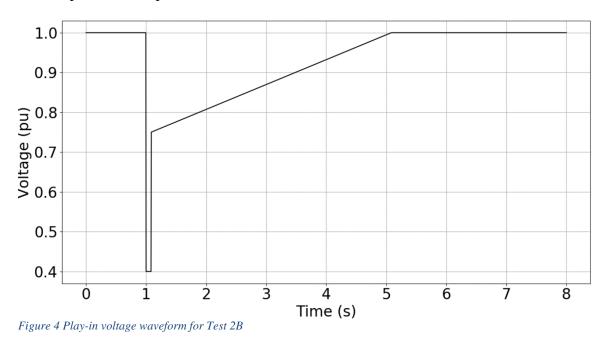

### Test Number 2B

The play-in waveform for this test is as shown in Figure 4. A voltage sag of 0.40 pu is applied at 1.0s for a duration of 5 cycles on 60 Hz. Immediately after that, the voltage is raised to 0.75 pu and ramped back to 1pu in 4s and run the simulation thereafter till 8s

### Test Number 3

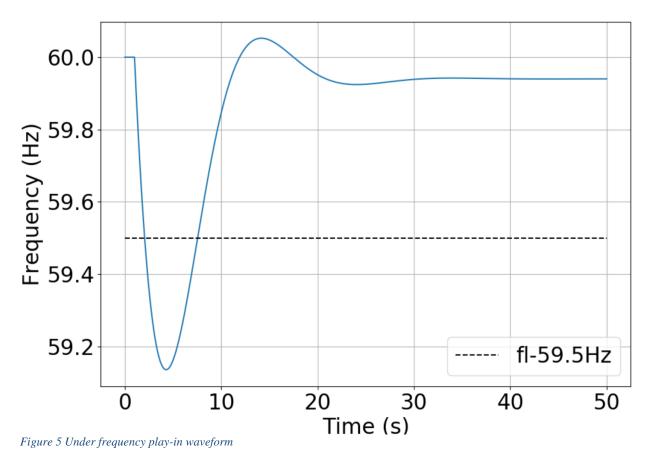

Figure 5 shows the frequency play-in waveforms to be used for test 3 while the equation provides details regarding the construction of the waveform

$$f(t) = \begin{cases} 60.0, & \text{for } 0.0 \le t < 1.0\\ A + B \exp^{-C(t-1.0)} \cos(D(t-1.0)) + E \exp^{-C(t-1.0)} \sin(D(t-1.0)), & \text{for } t \ge 1.0 \end{cases}$$

The values of the parameters A - E in the equation are tabulated in Table 3.

Table 3 Details of test frequency waveform

| Test | Α     | В    | С     | D      | Ε       |

|------|-------|------|-------|--------|---------|

| 3    | 59.94 | 0.06 | 0.199 | 0.3178 | -1.8246 |

## Test Number 4

The source at Bus 1 is represented by a classical machine model with MVA = 10000.0, H = 5.0s, and X'' = 0.2pu.

## References

[1] Bill Price and Shruti Rao, "CMPLDWG - DER-A Addition," WECC MVWG Meeting and NERC LMTF Meeting, January 2018 (<u>https://www.nerc.com/comm/PC/LoadModelingTaskForceDL/CMPLDW\_DER\_A\_Addition.pd</u> f) The parameter values for the DER\_A model are provided in **Error! Reference source not found.**. For the rest of the composite load model, NERC default parameters with stalling enabled will be used

| DESCRIPTION | UNITS    | Value    | DESCRIPTION                                                | Value |

|-------------|----------|----------|------------------------------------------------------------|-------|

|             |          |          | PfFlag; 1: constant power factor, 0: constant              |       |

| Trv         | (s),     | 0.02     | Q control                                                  | 1     |

|             |          |          | FreqFlag;                                                  |       |

|             |          | 0.07     | 1: frequency control enabled, 0: frequency                 |       |

| dbd1        | (pu),    | -0.05    | control disabled                                           | 1     |

| 11-10       | (        | 0.05     | PQflag; 1: P priority for current limit, 0: Q-             | 0     |

| dbd2        | (pu),    | 0.05     | priority<br>typeflag; 0: unit is a generator, 1: unit is a | 0     |

| Kqv         | (pu/pu), | 5        | storage device                                             | 0     |

| Kųv         | (pu/pu), | 5        | Vtripflag (flag to enable/disable voltage trip             | 0     |

|             |          |          | logic);                                                    |       |

| Vref0       | (pu),    | 0.0      | 1: enable, 0: disable                                      | 1     |

|             |          |          | Ftripflag (flag to enable/disable frequency                |       |

|             |          |          | trip logic);                                               |       |

| Тр          | (s),     | 0.02     | 1: enable, 0: disable                                      | 1     |

| Tiq         | (s),     | 0.02     |                                                            |       |

| Ddn         | (pu),    | 20.0     |                                                            |       |

| Dup         | (pu),    | 20.0     |                                                            |       |

|             |          | -        |                                                            |       |

| fdbd1       | (pu),    | 0.000283 |                                                            |       |

| fdbd2       | (pu),    | 0.000283 |                                                            |       |

| femax       | (pu),    | 99       |                                                            |       |

|             |          |          | All (pu) values for this model are                         |       |

| femin       | (pu),    | -99      | on a 12.47kV and 15.0 MVA base                             |       |

| PMAX        | (pu),    | 1.1      |                                                            |       |

| PMIN        | (pu),    | 0        |                                                            |       |

| dPmax       | (pu/s),  | 0.5      |                                                            |       |

| dPmin       | (pu/s),  | -0.5     |                                                            |       |

| Tpord       | (s),     | 0.02     |                                                            |       |

| Kpg         | (pu),    | 0.1      |                                                            |       |

| Kig         | (pu),    | 10       |                                                            |       |

| Imax        | (pu),    | 1.2      |                                                            |       |

| vl0         | (pu),    | 0.5      |                                                            |       |

| vl1         | (pu),    | 0.88     |                                                            |       |

| vh0     | (pu),    | 1.2   |

|---------|----------|-------|

| vh1     | (pu),    | 1.1   |

| tvl0    | (s),     | 0.1   |

| tvl1    | (s),     | 0.2   |

| tvh0    | (s),     | 0.1   |

| tvh1    | (s),     | 0.2   |

| Vrfrac, | fraction | 0.7   |

| fl      | (Hz),    | 59.5  |

| fh      | (Hz),    | 60.07 |

| tfl     | (s),     | 0.5   |

| tfh     | (s),     | 7.1   |

| Tg      | (s),     | 0.02  |

| rrpwr   | (pu/s),  | 0.5   |

| Tv      | (s),     | 0.02  |

| Xe      | (pu),    | 0.2   |

| Iqh1    | (pu)     | 0.5   |

| Iql1    | (pu)     | -0.5  |

| Vpr     | (pu)     | 0.8   |